# Steep-Slope WSe<sub>2</sub> Negative Capacitance Field-Effect Transistor

Mengwei Si, Chunsheng Jiang, Wonil Chung, Yuchen Du, Muhammad A. Alam, and Peide D. Ye\*

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, United States

Supporting Information

ABSTRACT: P-type two-dimensional steep-slope negative capacitance field-effect transistors are demonstrated for the first time with WSe2 as channel material and ferroelectric hafnium zirconium oxide in gate dielectric stack. F4-TCNQ is used as p-type dopant to suppress electron leakage current and to reduce Schottky barrier width for holes. WSe2 negative capacitance field-effect transistors with and without internal metal gate structures and the internal field-effect transistors are compared and studied. Significant SS reduction is observed in

WSe, negative capacitance field-effect transistors by inserting the ferroelectric hafnium zirconium oxide layer, suggesting the existence of internal amplification (~10) due to the negative capacitance effect. Subthreshold slope less than 60 mV/dec (as low as 14.4 mV/dec) at room temperature is obtained for both forward and reverse gate voltage sweeps. Negative differential resistance is observed at room temperature on WSe2 negative capacitance field-effect-transistors as the result of negative capacitance induced negative drain-induced-barrier-lowering effect.

KEYWORDS: Tungsten diselenide, negative capacitance, ferroelectric oxide, steep slope, internal metal gate

he so-called Boltzmann Tyranny (associated with the Boltzmann distribution of carriers) defines the fundamental thermionic limit of the subthreshold slope (SS) of a metal-oxide-semiconductor field-effect transistor (MOSFET) at 60 mV/dec at room temperature, which prohibits the decrease of the supply voltage and power consumption. Negative capacitance FETs (NC-FETs) have been proposed and attracted much attention to overcome this thermionic limit of SS. 1-14 In an NC-FET, the insulating ferroelectric material layer served as a negative capacitor so that channel surface potential can be amplified more than the gate voltage, and hence the device can operate with SS less than 60 mV/dec at room temperature. Transition metal dichalcogenides (TMDs) have been intensely explored as two-dimensional (2D) semiconductors for future device technologies because of the atomically ultrathin body for the ideal electrostatic control of the channel. It would be highly desirable to integrate ferroelectric insulator and 2D ultrathin channel materials as 2D NC-FETs to achieve subthermionic SS for low power dissipation and excellent immunity to short channel effects for transistor scaling. Very recently, n-type 2D NC-FETs with molybdenum disulfide (MoS<sub>2</sub>) as channel material and Si CMOS compatible Hf-based ferroelectric oxide as gate dielectric have been demonstrated with subthermionic SS at room temperature. However, both p-type and n-type FETs are required for complementary metal-oxide-semiconductor (CMOS) device technology but no p-type 2D NC-FETs with sub-60 mV/dec subthreshold slope was reported. Tungsten diselenide (WSe<sub>2</sub>) is one of the most studied TMDs as a highly promising p-type channel material, because of its balanced conduction and valence band edges and

high hole mobility. 15-22 Intrinsic WSe2 FETs usually exhibit ambipolar transport behavior due to the band alignment of metal to WSe2 near the middle of the bandgap, so that doping technique is required to obtain high performance WSe<sub>2</sub> transistors. P-type chemical doping in WSe2 such as NO2 and 2,3,5,6-tetrafluoro-7,7,8,8-tetracyanoquinodimethane (F4-TCNQ) has been studied to enhance the hole transport and to reduce the Schottky barrier width. 15,20

In this Letter, we demonstrate for the first time steep-slope p-type WSe<sub>2</sub> NC-FETs by combining ferroelectric hafnium zirconium oxide (HZO) gate stack and F4-TCNQ p-type chemical doping. The effect of internal metal gate (IMG) on the performance of WSe<sub>2</sub> NC-FET is also studied by inserting a metal layer between ferroelectric HZO and the positive gate oxide. For WSe<sub>2</sub> NC-FET without IMG and after F4-TCNQ doping, minimum SS of 40.2 mV/dec and less than 60 mV/dec are achieved for both forward and reverse gate-to-source voltage  $(V_{GS})$  sweeps on the p-type WSe<sub>2</sub> NC-FETs with a low hysteresis of less than 0.2 V. For WSe<sub>2</sub> NC-FETs without IMG and before F4-TCNQ doping, the transistors exhibit ambipolar transport behavior and a high drain current  $(I_D)$  is achieved on nFET due to the enhanced electric field from the ferroelectricity in the gate oxide. Negative differential resistance (NDR), correlated to the drain coupled negative capacitance effect, is also observed on both n-type and p-type NC-FETs. For WSe<sub>2</sub> NC-FET with IMG and after F4-TCNQ doping,  $SS_{For}$  = 41.2 mV/dec and  $SS_{Rev}$  = 14.4 mV/dec are achieved

Received: February 27, 2018 Revised: April 14, 2018 Published: May 7, 2018

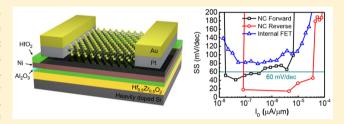

Figure 1. (a) Schematic view of a WSe $_2$  NC-FET without IMG. The gate stack includes the heavily doped Si as gate electrode, 20 nm HZO as the ferroelectric capacitor, and 2 nm  $Al_2O_3$  as capping layer. The 30 nm Pt/50 nm Au are used as source/drain electrodes. (b) Schematic view of a WSe $_2$  NC-FET with IMG. The gate stack includes the heavily doped Si as gate electrode, 20 nm HZO, 3 nm  $Al_2O_3$ , 20 nm Ni as IMG, and 10 nm HfO $_2$  as the gate dielectric for internal FET. The 30 nm Pt/50 nm Au are used as source/drain electrodes. (c) False-color top-view SEM image of a representative WSe $_2$  NC-FET. (d) Polarization versus electric field for ferroelectric MIM (TiN/10 nm HZO/TiN) capacitor with 500 °C RTA and without RTA. HZO exhibits clear ferroelectricity after 500 °C annealing.

with negative hysteresis due to the ferroelectric switching, while the SS of internal WSe<sub>2</sub> FET is 79.1 mV/dec. The SS of the WSe<sub>2</sub> NC-FET with IMG is much smaller than the SS measured from the internal WSe<sub>2</sub> FET, suggesting the existence of internal amplification by the ferroelectric HZO.

The experimental device schematic of a WSe<sub>2</sub> NC-FET without IMG is shown in Figure 1a, which consists of few-layer WSe<sub>2</sub> as channel, 2 nm amorphous aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) layer and 20 nm polycrystalline HZO layer as the gate dielectric, heavily doped silicon substrate as the gate electrode and Pt/Au source/drain contacts. The device schematic of a WSe<sub>2</sub> NC-FET with IMG is shown in Figure 1b, which consists of few-layer WSe2 as channel, 20 nm polycrystalline HZO, 3 nm amorphous Al<sub>2</sub>O<sub>3</sub>, 20 nm Ni layer as IMG and 10 nm HfO<sub>2</sub> as gate dielectric of internal FET, heavily doped silicon substrate as the gate electrode and Pt/Au source/drain contacts. HZO was deposited by atomic layer deposition (ALD) as a ferroelectric insulator layer<sup>23</sup> on a heavily doped silicon substrate after standard solvent clean and hydrogen fluoride passivation. Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> film was deposited at 250 °C, using  $[(CH_3)_2N]_4Hf$  (TDMAHf),  $[(CH_3)_2N]_4Zr$  (TDMAZr), and H<sub>2</sub>O as the Hf precursor, Zr precursor, and O precursor, respectively. The  $Hf_{1-x}Zr_xO_2$  film with x = 0.5 was achieved by controlling HfO<sub>2</sub>/ZrO<sub>2</sub> cycle ratio to be 1:1. Another 2 or 3 nm Al<sub>2</sub>O<sub>3</sub> layer was in situ deposited at 250 °C, using Al(CH<sub>3</sub>)<sub>3</sub> as Al precursor and H<sub>2</sub>O as oxygen precursor, as an encapsulation layer to prevent the degradation of HZO by the reaction with moisture in air and the amorphous Al<sub>2</sub>O<sub>3</sub> layer was also used for capacitance matching and gate leakage current reduction through polycrystalline HZO. A rapid thermal annealing (RTA) in nitrogen ambient was then performed for 1 min at 500 °C to enhance the ferroelectricity, as shown in Figure 1d. Clear dielectric to ferroelectric transition can be seen after annealing on the metal-insulator-metal (MIM, TiN/10 nm HZO/TiN)

capacitor. As the working speed of NC-FETs is directly related with the ferroelectric polarization switching speed, the MIM capacitor structure is also used in high-frequency measurement up to 0.5 MHz to study the time response of ferroelectric switching in HZO, as shown in Figure 2 and in Supporting

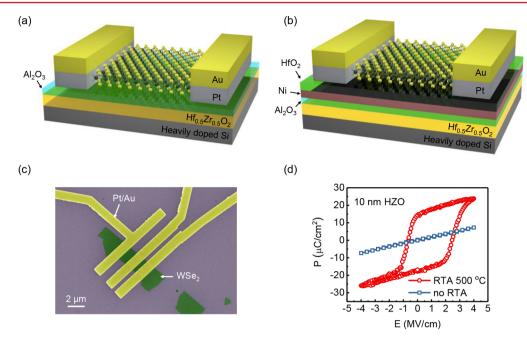

**Figure 2.** (a) Polarization versus electric field hysteresis loop of a TiN/10 nm HZO/TiN capacitor measured by a Radiant RT66C ferroelectric tester from 50 Hz to 1 kHz. (b) Polarization versus electric field hysteresis loop of the same capacitor measured using RC circuit and arbitrary function generator (square wave).

Information (SI) Section 1. For WSe<sub>2</sub> NC-FETs with IMG, the IMG pattern was then defined by electron-beam lithography, followed by 20 nm Ni electron-beam evaporation and lift-off process. Another 10 nm HfO<sub>2</sub> was deposited by ALD at 250 °C using TDMAHf and H<sub>2</sub>O as precursors. WSe<sub>2</sub> flakes were then transferred to the substrate by scotch tape-based mechanical exfoliation from a bulk crystal (Nanosurf, Inc.). Electrical contacts using 30 nm Pt and 50 nm Au electrodes were fabricated using electron-beam lithography, electron-beam evaporation, and lift-off process. A false-color top-view scanning electron microscopy (SEM) image of a representative WSe<sub>2</sub> NC-FET is shown in Figure 1c, capturing the Pt/Au source/drain electrodes and the WSe<sub>2</sub> flakes. Electrical measurement

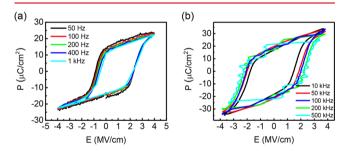

Figure 3. (a) Cross-sectional view of WSe<sub>2</sub> NC-FETs without internal metal gate. (b)  $I_{\rm D}-V_{\rm GS}$  in 20 mV  $V_{\rm GS}$  step and (c)  $I_{\rm D}-V_{\rm DS}$  characteristics of a WSe<sub>2</sub> NC-FET before F4-TCNQ doping. This device has a channel length of 0.5  $\mu$ m and channel thickness of 5.5 nm. A high maximum drain current of 239  $\mu$ A/ $\mu$ m is achieved. Clear NDR can be observed in  $I_{\rm D}-V_{\rm DS}$  characteristics because of the negative DIBL effect induced by negative capacitance. (d)  $I_{\rm D}-V_{\rm GS}$  in 50 mV  $V_{\rm GS}$  step and (e)  $I_{\rm D}-V_{\rm DS}$  characteristics of WSe<sub>2</sub> NC-FETs after F4-TCNQ doping. This device has a channel length of 1  $\mu$ m and channel thickness of 6.1 nm. The device exhibits SS<sub>Rev</sub> = 40.2 mV/dec, SS<sub>For</sub> = 57.5 mV/dec at  $V_{\rm DS}$  = -0.1 V. SS below 60 mV/dec at room temperature is demonstrated for both forward and reverse gate voltage sweeps. Clear NDR can be observed in  $I_{\rm D}-V_{\rm DS}$  characteristics because of the negative DIBL effect induced by negative capacitance. (f) SS versus  $I_{\rm D}$  characteristics of p-type WSe<sub>2</sub> NC-FET without IMG and after F4-TCNQ doping, of the same device as in panel d.

was first carried out on the completed WSe2 NC-FETs. The measured sample was then soaked in an isopropyl alcohol solution of 0.75 mmol/L F4-TCNQ for 12 h followed by N2 drying for p-type doping of the channel. F4-TCNQ is an organic molecule with a large electron affinity of 5.2 eV. It is widely used as a p-type dopant for graphene, black phosphorus, TMDs and other low dimensional materials. 20,24-26 doping, the WSe2 NC-FETs were electrically characterized again under ambient condition. All electrical measurements were carried out at room temperature. The I-V measurement was done using a B1500 system with HRSMU and with HR-ADC in AUTO mode. The time in I-V measurement for each data point can be calculated as time = default integration time  $\times$  factor, where factor = 20 in this work. Default integration time is related with the current level and can be found from the B1500 manual. Estimated time constants for different current levels are listed as following, 1 pA, 25.6 ms; 10 pA, 25.6 ms; 100 pA, 12.8 ms; 1 nA, 6.4 ms; 10 nA, 6.4 ms; 100 nA, 16 ms; 1  $\mu$ A, 1.6 ms; 10  $\mu$ A, 3.2 ms; 100  $\mu$ A, 1.6 ms.

To study the ferroelectric property of the gate stack, especially the ferroelectric switching at high speed, ferroelectric MIM (TiN/10 nm HZO/TiN) capacitors are used as test structure. The polarization versus electric field (P-E) characteristics is measured in two different ways. At low frequency from 50 Hz to 1 kHz, P-E is measured by a Radiant RT66C ferroelectric tester (voltage sweep), as shown in Figure 2a. At high frequency from 10 kHz to 0.5 MHz, P-E is measured (Figure 2b) based on the transient response to square wave voltage signal in RC circuit, which is discussed in detail in SI Section 1. The P-E shows clear ferroelectric switching up to 0.5 MHz. The measurement at high frequency above 0.1 MHz becomes noisier because of the bandwidth of the measurement system. Therefore, the frequency-dependent

measurement here confirmed that in ferroelectric HZO, the ferroelectric switching speed can be at least at megahertz level but the upper limit of ferroelectric switching speed has not been detected by current experimental setup.

The electrical performance of WSe<sub>2</sub> NC-FET without IMG is shown in Figure 3. Figure 3a shows the cross-sectional view of a WSe<sub>2</sub> NC-FET without IMG. The  $I_D$ - $V_{GS}$  characteristics of a WSe<sub>2</sub> NC-FET before F4-TCNQ doping is shown in Figure 3b. This device has a channel length  $(L_{ch})$  of 0.5  $\mu$ m and channel thickness  $(T_{ch})$  of 5.5 nm, measured by atomic force microscopy (AFM). The  $I_{\rm D} - V_{\rm GS}$  characteristics were measured in bidirection forwardly ( $V_{GS}$  from high to low) and reversely ( $V_{GS}$  from low to high) in 20 mV  $V_{GS}$  step. SS is extracted for both forward sweep  $(SS_{For})$  and reverse sweep  $(SS_{Rev})$  at low  $V_{DS}$ . The device exhibits  $SS_{For} = 249.9 \text{ mV/dec}$ ,  $SS_{Rev} = 176.0$ mV/dec for nFET and the device exhibits  $SS_{For} = 297.4 \text{ mV/}$ dec,  $SS_{Rev} = 225.8 \text{ mV/dec}$  for pFET. Figure 3c shows  $I_D - V_{DS}$ characteristics of the same WSe<sub>2</sub> NC-FET as shown in Figure 3b. The gate voltage is stressed up to 10.5 V and maximum gate voltage over EOT in this device is about 2.4 V/nm. A high maximum drain current of 239  $\mu$ A/ $\mu$ m is achieved. The similar on-state performance enhancement on MoS2 nFETs and black phosphorus pFETs were also observed in our previous works. 11,27 By applying ferroelectric gate stack, on-state performance of 2D FETs is significantly enhanced. SS is far above the thermionic limit at room temperature for two reasons. First, the ambipolar transport, which means electron current overwhelms hole current in the off-state of pFET while hole current overwhelms electron current in the off-state of nFET, prevents the device deeply into off-state from gate control. Second, SS is degraded by the impact of the large Schottky barriers for both electrons and holes.<sup>28</sup> Therefore,

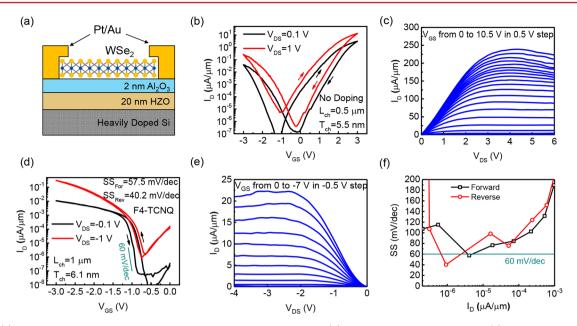

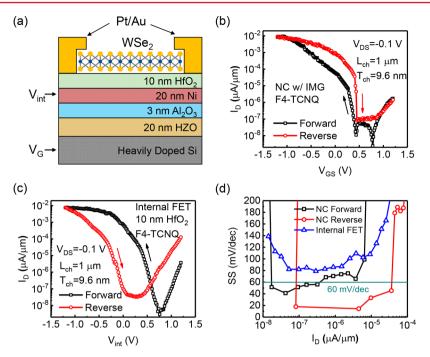

Figure 4. (a) Cross-sectional view of WSe<sub>2</sub> NC-FETs with internal metal gate. (b)  $I_{\rm D}$ – $V_{\rm GS}$  characteristics in 20 mV  $V_{\rm GS}$  step of a representative WSe<sub>2</sub> NC-FET with IMG and after F4-TCNQ doping. This device has a channel length of 1  $\mu$ m and channel thickness of 9.6 nm. The device exhibits SS<sub>Rev</sub> = 14.4 mV/dec, SS<sub>For</sub> = 41.2 mV/dec at  $V_{\rm DS}$  = -0.1 V. SS below 60 mV/dec at room temperature is demonstrated for both forward and reverse gate voltage sweeps. (c)  $I_{\rm D}$ – $V_{\rm GS}$  characteristics in 20 mV  $V_{\rm GS}$  step of the internal WSe<sub>2</sub> FET of the same device as in Figure 4b. The device exhibits SS = 79.1 mV/dec (d) SS versus  $I_{\rm D}$  characteristics of p-type WSe<sub>2</sub> NC-FET with IMG and the internal WSe<sub>2</sub> FET.

suppressing the ambipolar effect and reducing the Schottky barriers are the keys to reduce SS in WSe<sub>2</sub> NC-FETs.

F4-TCNQ was applied to WSe2 to realize p-type channel doping. With p-type dopant in channel, the electron carrier density inside the WSe2 channel is significantly reduced and electron branch is suppressed. Meanwhile, the Schottky barrier width for hole transport is reduced, which leads to the reduction of contact resistance and the enhancement of hole branch and on-current for pFETs. Figure 3d shows the  $I_D$ - $V_{GS}$ characteristics of a typical WSe<sub>2</sub> p-type NC-FET with F4-TCNQ doping in 50 mV VGS step. This device has a channel length of 1  $\mu$ m, and channel thickness of 6.1 nm, measured by AFM. The device exhibits  $SS_{Rev} = 40.2 \text{ mV/dec}$ ,  $SS_{For} = 57.5$ mV/dec SS below 60 mV/dec at room temperature is demonstrated for both forward and reverse gate voltage sweeps, as shown in Figure 3f. SS of p-type NC-FET below the thermionic limit is the result of the negative capacitance effect. Meanwhile, a low hysteresis (defined as  $V_{GS}$  difference at 1 pA/  $\mu$ m in  $I_D$ – $V_{GS}$  characteristics) of 0.18 V is also obtained. Figure 3e shows  $I_D$ – $V_{DS}$  characteristics of the same WSe<sub>2</sub> NC-FET as shown in Figure 3d. In conventional MOSFETs, the threshold voltage  $(V_{th})$  shifts toward the negative direction as drain voltage. The drain-induced-barrier-lowering (DIBL), defined as DIBL =  $-\Delta V_{\rm th}/\Delta V_{\rm DS}$ , is usually positive. With ferroelectric gate stack, the DIBL effect could be reversed in NC-FETs. 29,30 The negative DIBL origins from the negative capacitance coupling from drain to the interfacial layer between Al<sub>2</sub>O<sub>3</sub> and HZO. NDR can naturally occur as a result of the negative DIBL effect because the positive drain voltage can induce negative charge into the channel. NDR is observed for both WSe<sub>2</sub> n-type NC-FET and p-type NC-FET, as shown in Figure 3c,e, indicating the effectiveness of the negative capacitance effect in ferroelectric HZO.

The electrical performance of WSe<sub>2</sub> NC-FET with IMG and after F4-TCNQ doping is shown in Figure 4. Figure 4a shows the cross-sectional view of a WSe2 NC-FET with IMG. The IMG here is used to enhance the negative capacitance effect for SS reduction. Figure 4b shows the  $I_{\rm D}{-}V_{\rm GS}$  characteristics of a WSe<sub>2</sub> p-type NC-FET with IMG and after F4-TCNQ doping (IMG floating) in 20 mV V<sub>GS</sub> step. This device has a channel length of 1  $\mu$ m, and channel thickness of 9.6 nm. The device exhibits  $SS_{Rev} = 14.4 \text{ mV/dec}$ ,  $SS_{For} = 41.2 \text{ mV/dec}$ , and a negative hysteresis of -0.12 V (at  $I_D = 1$  pA/ $\mu$ m). Figure 4c shows the  $I_{\rm D} - V_{\rm GS}$  characteristics of the internal WSe<sub>2</sub> FET of the same device as in Figure 4b, using IMG as gate electrode in 20 mV  $V_{GS}$  step. Figure 4d shows SS versus  $I_D$  characteristics in the off-state of  $I_D$ – $V_{GS}$  characteristics in Figure 4b,c. SS below 60 mV/dec at room temperature is demonstrated for both forward and reverse gate voltage sweeps, suggesting the existence of internal amplification. The internal amplification, defined as  $dV_{int}/dV_{GS}$ , is calculated to be 10/1.8 for reverse/ forward gate voltage sweep. Note that the positive hysteresis of the internal WSe2 FET, as shown in Figure 4c, is induced by trapping and detrapping process in the gate oxide or the oxide/ semiconductor interface. This positive hysteresis is much larger compared with WSe<sub>2</sub> NC-FET shown in Figure 3d, suggesting the existence of negative capacitance/ferroelectric effect in the gate stack, which leads to the reduction of positive hysteresis.

In conclusion, WSe<sub>2</sub> NC-FETs with ferroelectric HZO gate stack are demonstrated. Chemical doping of F4-TCNQ is applied to suppress the electron current in the off-state of p-type NC-FETs and to reduce the Schottky barrier width for holes. The doped devices exhibit steep-slope switching characteristics with less than 60 mV/dec for bidirectional sweeps. Sub-60 mV/dec SS (as low as 14.4 mV/dec) and negative DIBL effect conclusively confirm the realization of

negative capacitance effect in WSe<sub>2</sub> 2D-FETs with HZO as gate dielectric.

#### ASSOCIATED CONTENT

## **S** Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acs.nanolett.8b00816.

Additional details for transient RC measurement of ferroelectric HZO, statistical and cycling measurement of HZO MIM capacitor, gate stack leakage current, detailed numerical simulation, and modeling of enhancement by IMG (PDF)

### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: yep@purdue.edu.

ORCID @

Mengwei Si: 0000-0003-0397-7741 Peide D. Ye: 0000-0001-8466-9745

#### **Author Contributions**

P.D.Y. conceived the idea and supervised the experiments. M.S. did the device fabrication, DC electrical measurement and analysis. M.S. and W.C. did the P–E measurement. C.J. and M.A.A. conducted numerical simulation. M.S. and Y.D. performed the F4-TCNQ doping. M.S. and P.D.Y. cowrote the manuscript and all authors commented on it.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors would like to thank C.-J. Su, S. Salahuddin, and H. Ota for valuable discussions.

#### REFERENCES

- (1) Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. *Nano Lett.* **2008**, *8*, 405–410.

- (2) Salvatore, G. A.; Bouvet, D.; Ionescu, A. M. Demonstration of Subthrehold Swing Smaller Than 60mV/decade in Fe-FET with P(VDF-TrFE)/SiO<sub>2</sub> Gate Stack. *IEEE Int. Electron Devices Meet.* **2008**, 167–170

- (3) Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; Chen, M.-C.; Sheih, J.-M.; Yeh, W.-K.; Yang, F.-L.; Salahuddin, S.; Hu, C. Sub-60mV-Swing Negative-Capacitance FinFET without Hysteresis. *IEEE Int. Electron Devices Meet.* **2015**, 620–623.

- (4) Khan, A. I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S. R.; Ramesh, R.; Salahuddin, S. Negative Capacitance in a Ferroelectric Capacitor. *Nat. Mater.* **2015**, *14*, 182–186.

- (5) Zhou, J.; Han, G.; Li, Q.; Peng, Y.; Lu, X.; Zhang, C.; Zhang, J.; Sun, Q.-Q.; Zhang, D. W.; Hao, Y. Ferroelectric HfZrO<sub>x</sub> Ge and GeSn PMOSFETs with Sub-60 mV/decade Subthreshold Swing, Negligible Hysteresis, and Improved I<sub>DS</sub>. *IEEE Int. Electron Devices Meet.* **2016**, 310–313.

- (6) Lee, M. H.; Fan, S.-T.; Tang, C.-H.; Chen, P.-G.; Chou, Y.-C.; Chen, H.-H.; Kuo, J.-Y.; Xie, M.-J.; Liu, S.-N.; Liao, M.-H.; Jong, C.-A.; Li, K.-S.; Chen, M.-C.; Liu, C. W. Physical Thickness 1.x nm Ferroelectric HfZrOx Negative Capacitance FETs. *IEEE Int. Electron Devices Meet.* **2016**, 306–309.

- (7) Krivokapic, Z.; Rana, U.; Galatage, R.; Razavieh, A.; Aziz, A.; Liu, J.; Shi, J.; Kim, H. J.; Sporer, R.; Serrao, C.; Busquet, A.; Polakowski, P.; Müller, J.; Kleemeier, W.; Jacob, A.; Brown, D.; Knorr, A.; Carter,

R.; Banna, S. 14nm Ferroelectric FinFET Technology with Steep Subthreshold Slope for Ultra Low Power Applications. *IEEE Int. Electron Devices Meet.* **2017**, 357–360.

- (8) Sharma, P.; Zhang, J.; Ni, K.; Datta, S. Time-Resolved Measurement of Negative Capacitance. *IEEE Electron Device Lett.* **2018**, 39, 272–275.

- (9) Chung, W.; Si, M.; Ye, P. D. Hysteresis-Free Negative Capacitance Germanium CMOS FinFETs with Bi-directional Sub-60 mV/dec. *IEEE Int. Electron Devices Meet.* **2017**, 365–368.

- (10) McGuire, F. A.; Lin, Y.-C.; Price, K.; Rayner, G. B.; Khandelwal, S.; Salahuddin, S.; Franklin, A. D. Sustained Sub-60 mV/decade Switching via the Negative Capacitance Effect in  $MoS_2$  Transistors. *Nano Lett.* **2017**, *17*, 4801–4806.

- (11) Si, M.; Su, C.-J.; Jiang, C.; Conrad, N. J.; Zhou, H.; Maize, K. D.; Qiu, G.; Wu, C.-T.; Shakouri, A.; Alam, M. A.; Ye, P. D. Steep-Slope Hysteresis-Free Negative Capacitance MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2018**, *13*, 24–28.

- (12) Si, M.; Jiang, C.; Su, C.-J.; Tang, Y.-T.; Yang, L.; Chung, W.; Alam, M. A.; Ye, P. D. Sub-60 mV/dec Ferroelectric HZO MoS<sub>2</sub> Negative Capacitance Field-Effect Transistor with Internal Metal Gate: The Role of Parasitic Capacitance. *IEEE Int. Electron Devices Meet.* **2017**, 573–576.

- (13) Nourbakhsh, A.; Zubair, A.; Joglekar, S. J.; Dresselhaus, M. S.; Palacios, T. Subthreshold Swing Improvement in MoS<sub>2</sub> Transistors by the Negative-Capacitance Effect in a Ferroelectric Al-doped-HfO<sub>2</sub>/HfO<sub>2</sub> Gate Dielectric Stack. *Nanoscale* **2017**, *9*, 6122–6127.

- (14) Yu, Z.; Wang, H.; Li, W.; Xu, S.; Song, X.; Wang, S.; Wang, P.; Zhou, P.; Shi, Y.; Chai, Y.; Wang, X. Negative Capacitance 2D  $MoS_2$  Transistors with Sub-60mV/dec Subthreshold Swing Over 6 Orders, 250  $\mu$ A/ $\mu$ m Current Density, and Nearly-Hysteresis-Free. *IEEE Int. Electron Devices Meet.* **2017**, 577–580.

- (15) Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- (16) Liu, W.; Kang, J.; Sarkar, D.; Khatami, Y.; Jena, D.; Banerjee, K. Role of Metal Contacts in Designing High-Performance Monolayer ntype WSe<sub>2</sub> Field Effect Transistors. *Nano Lett.* **2013**, *13*, 1983–1990.

- (17) Das, S.; Appenzeller, J. WSe<sub>2</sub> Field Effect Transistors with Enhanced Ambipolar Characteristics. *Appl. Phys. Lett.* **2013**, 103, 103501.

- (18) Huang, J.-K.; Pu, J.; Hsu, C.-L.; Chiu, M.-H.; Juang, Z.-Y.; Chang, Y.-H.; Chang, W.-H.; Iwasa, Y.; Takenobu, T.; Li, L.-J. Large-Area Synthesis of Highly Crystalline WSe<sub>2</sub> Monolayers and Device Applications. *ACS Nano* **2014**, *8*, 923–930.

- (19) Chuang, H.-J.; Tan, X.; Ghimire, N. J.; Perera, M. M.; Chamlagain, B.; Cheng, M. M.-C.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. High Mobility WSe<sub>2</sub> p- and n- Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. *Nano Lett.* **2014**, *14*, 3594–3601.

- (20) Yu, L.; Zubair, A.; Santos, E. J. G.; Zhang, X.; Lin, Y.; Zhang, Y.; Palacios, T. High-Performance WSe<sub>2</sub> Complementary Metal Oxide Semiconductor Technology and Integrated Circuits. *Nano Lett.* **2015**, 15, 4928–4934.

- (21) Shen, T.; Penumatcha, A. V.; Appenzeller, J. Strain Engineering for Transition Metal Dichalcogenides Based Field Effect Transistors. *ACS Nano* **2016**, *10*, 4712–4718.

- (22) Chuang, H.-J.; Chamlagain, B.; Koehler, M.; Perera, M. M.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. Low-Resistance 2D/2D Ohmic Contacts: A Universal Approach to High-Performance WSe<sub>2</sub>, MoS<sub>2</sub>, and MoSe<sub>2</sub> Transistors. *Nano Lett.* **2016**, *16*, 1896–1902.

- (23) Muller, J.; Boscke, T. S.; Schroder, U.; Mueller, S.; Brauhaus, D.; Bottger, U.; Frey, L.; Mikolajick, T. Ferroelectricity in Simple Binary ZrO<sub>2</sub> and HfO<sub>2</sub>. *Nano Lett.* **2012**, *12*, 4318–4323.

- (24) Liu, H.; Liu, Y.; Zhu, D. Chemical Doping of Graphene. *J. Mater. Chem.* **2011**, *21*, 3335–3345.

- (25) Du, Y.; Yang, L.; Zhou, H.; Ye, P. D. Performance Enhancement of Black Phosphorus Field-Effect Transistors by Chemical Doping. *IEEE Electron Device Lett.* **2016**, *37*, 429–432.

(26) Chen, W.; Chen, S.; Qi, D. C.; Gao, X. Y.; Wee, A. T. S. Surface Transfer p-type Doping of Epitaxial Graphene. *J. Am. Chem. Soc.* **2007**, 129, 10418–10422.

- (27) Si, M.; Yang, L.; Du, Y.; Ye, P. D. Black Phosphorus Field-Effect Transistor with Record Drain Current Exceeding 1 A/mm. In 75th Annual Device Research Conference; 2017.

- (28) Appenzeller, J.; Knoch, J.; Derycke, V.; Martel, R.; Wind, S.; Avouris, P. Field-Modulated Carrier Transport in Carbon Nanotube Transistors. *Phys. Rev. Lett.* **2002**, *89*, 126801.

- (29) Ota, H.; Ikegami, T.; Hattori, J.; Fukuda, K.; Migita, S.; Toriumi, A. Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs for Sub 10 nm Integration. *IEEE Int. Electron Devices Meet.* **2016**, 318–321.

- (30) Duarte, J. P.; Khandelwal, S.; Khan, A. I.; Sachid, A.; Lin, Y.-K.; Chang, H.-L.; Salahuddin, S.; Hu, C. Compact Models of Negative-Capacitance FinFETs: Lumped and Distributed Charge Models. *IEEE Int. Electron Devices Meet.* **2016**, 318–321.